笔记——设置FPGA的Siginal Tap和用Nios烧录程序

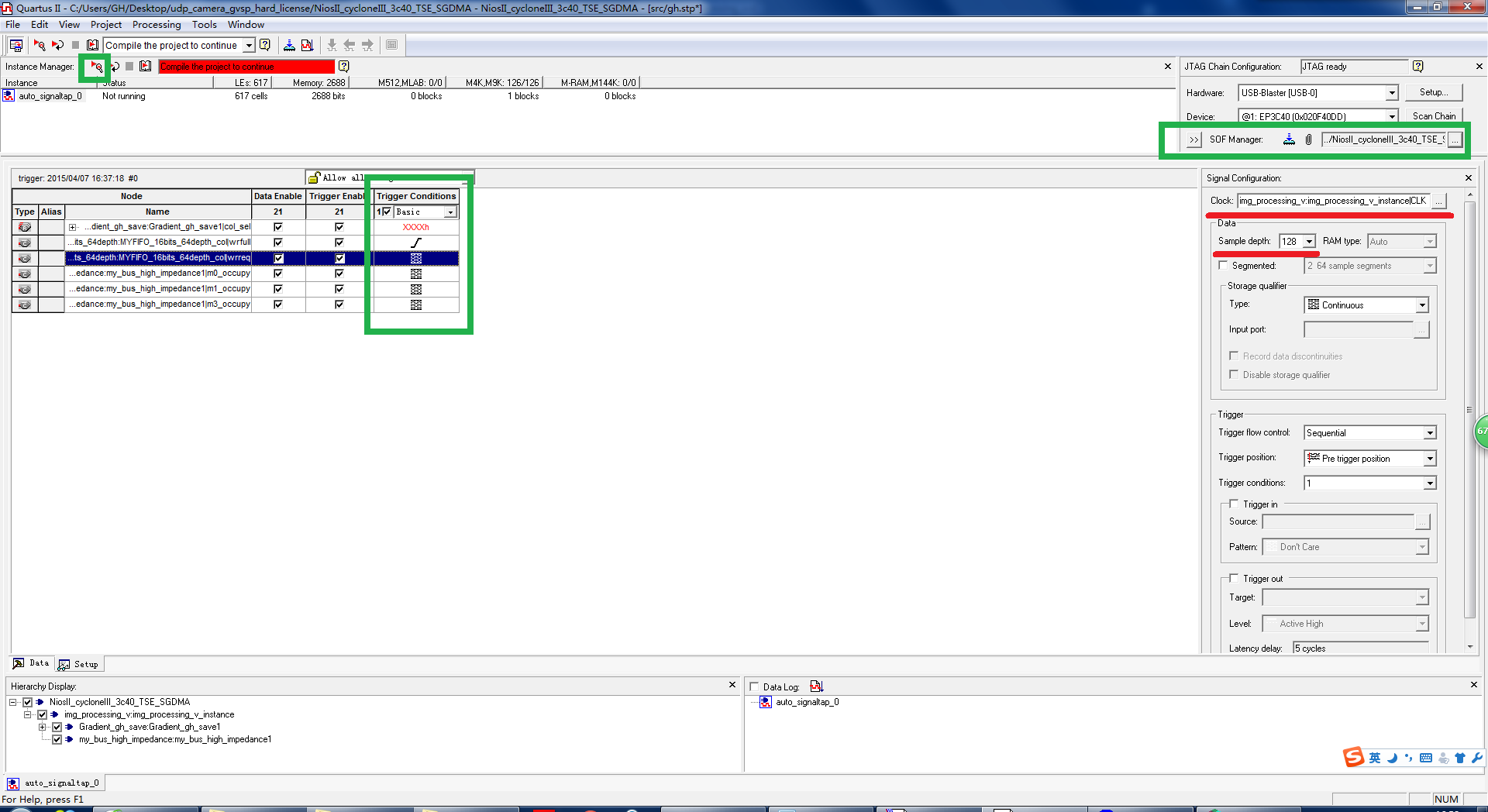

SignalTap的使用

- 打开SignalTap后在setup中设置需要跟踪查看的变量;

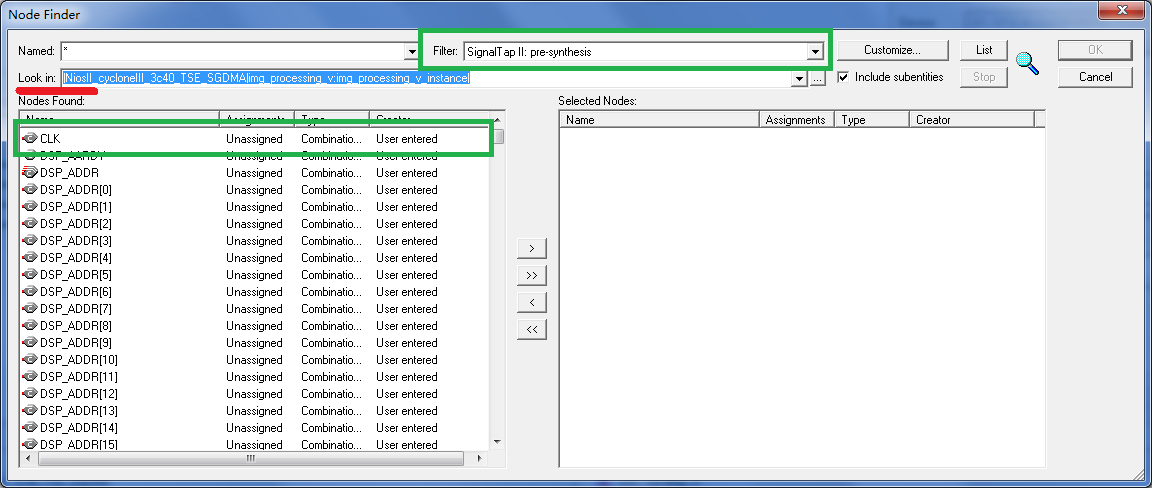

- Filter选择pre-synthesis, named一般不好用,所以在lookin中选择变量所在的模块,点击list,找到后双击勾选到右侧方框;

- 右侧的时钟模块勾选系统计算所依赖的CLK;

- Data中的Sample depth表示的是需要查看多长的波形,选择过大会导致FPGA资源不够用,编译无法通过;

- 设置好之后,在触发条件处勾选上升沿或下降沿出发,当选择两个以上的变量的触发条件时,表示的是两个条件同时发生才会记录波形;

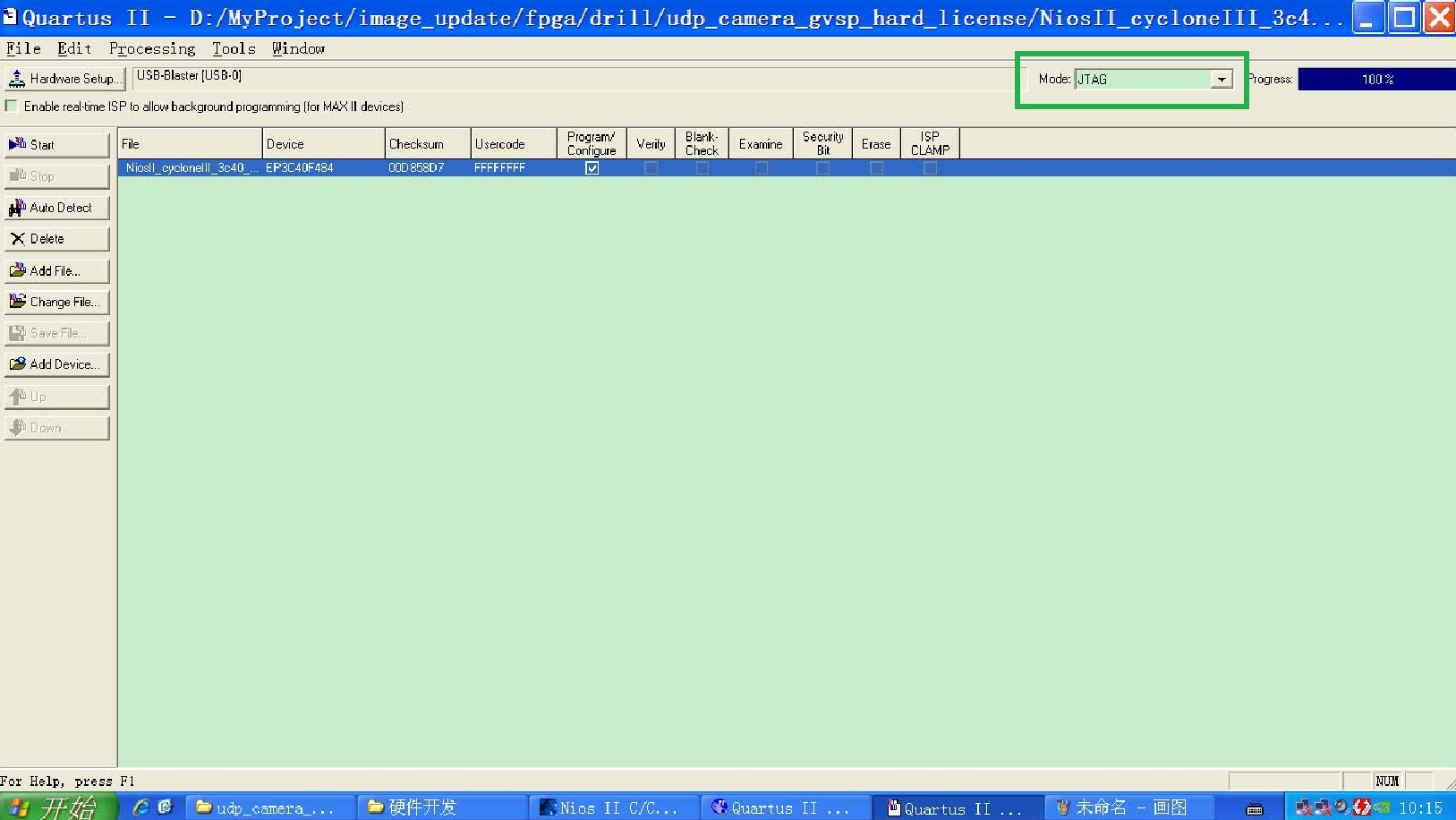

- 之后编译FPGA程序,点击SOFmanager的 device programmer,把程序下载到芯片;

- 下载DSP程序,运行,在SignalTap中点击Run analysis。

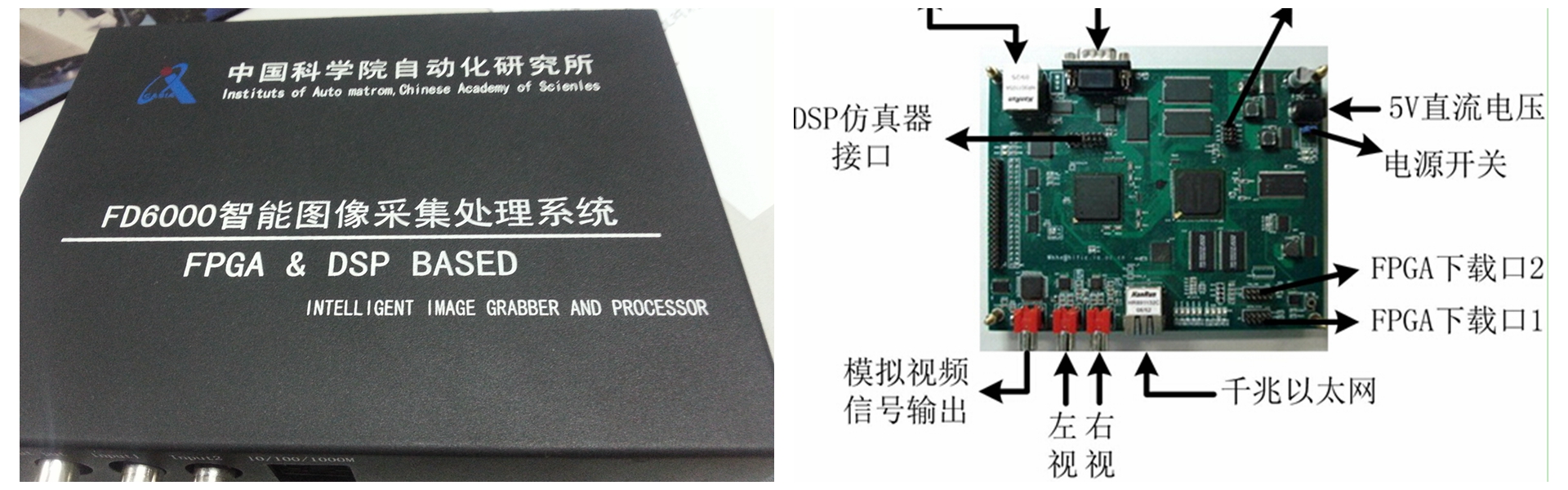

通过Nios下载数字摄像头程序到FPGA中

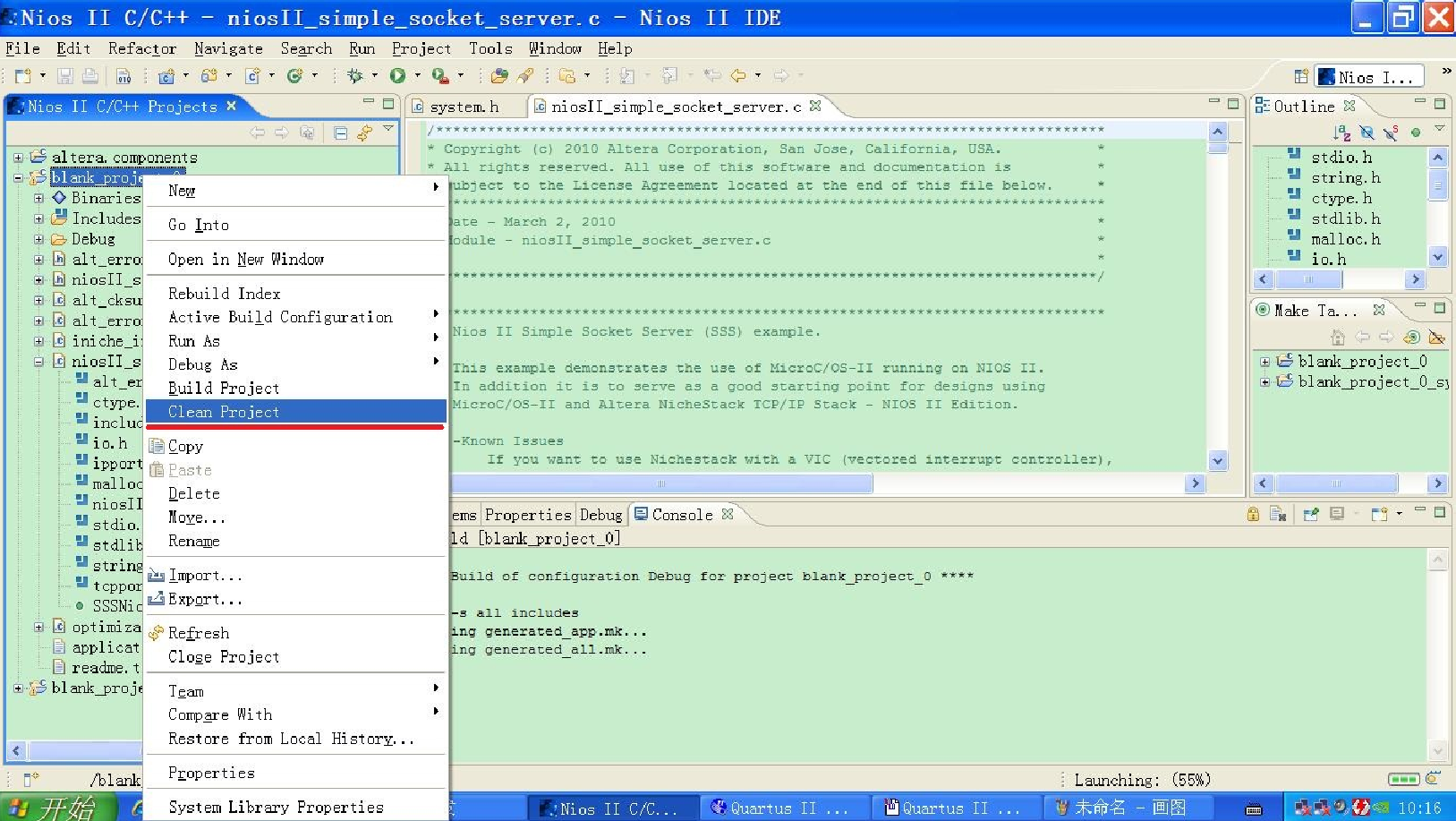

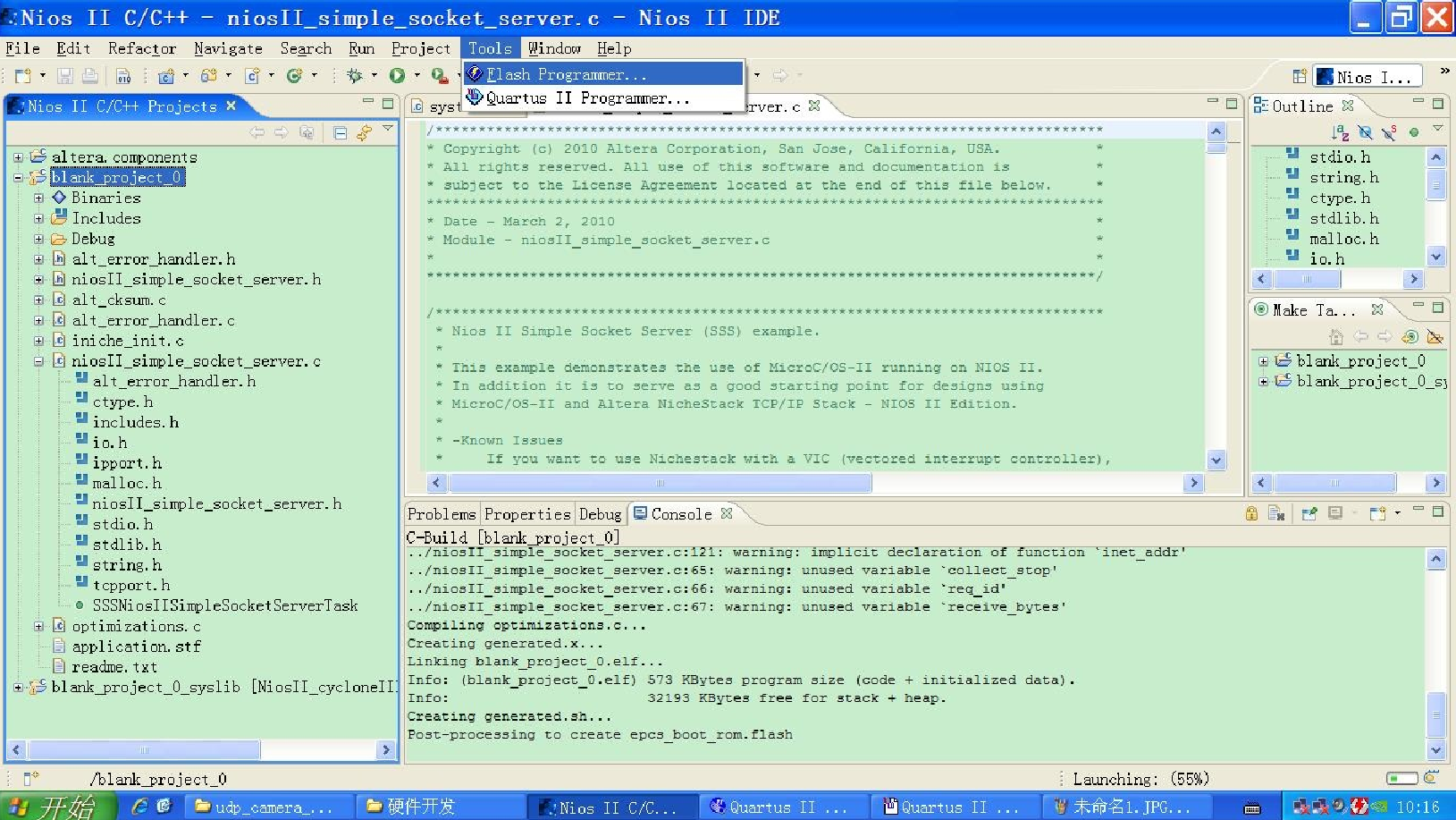

- 在Quartus中把编译好的程序用Jtag方式下载(烧录模拟摄像头时是需要在Active_serial方式下烧录的),之后打开Nios,clean project,build project;

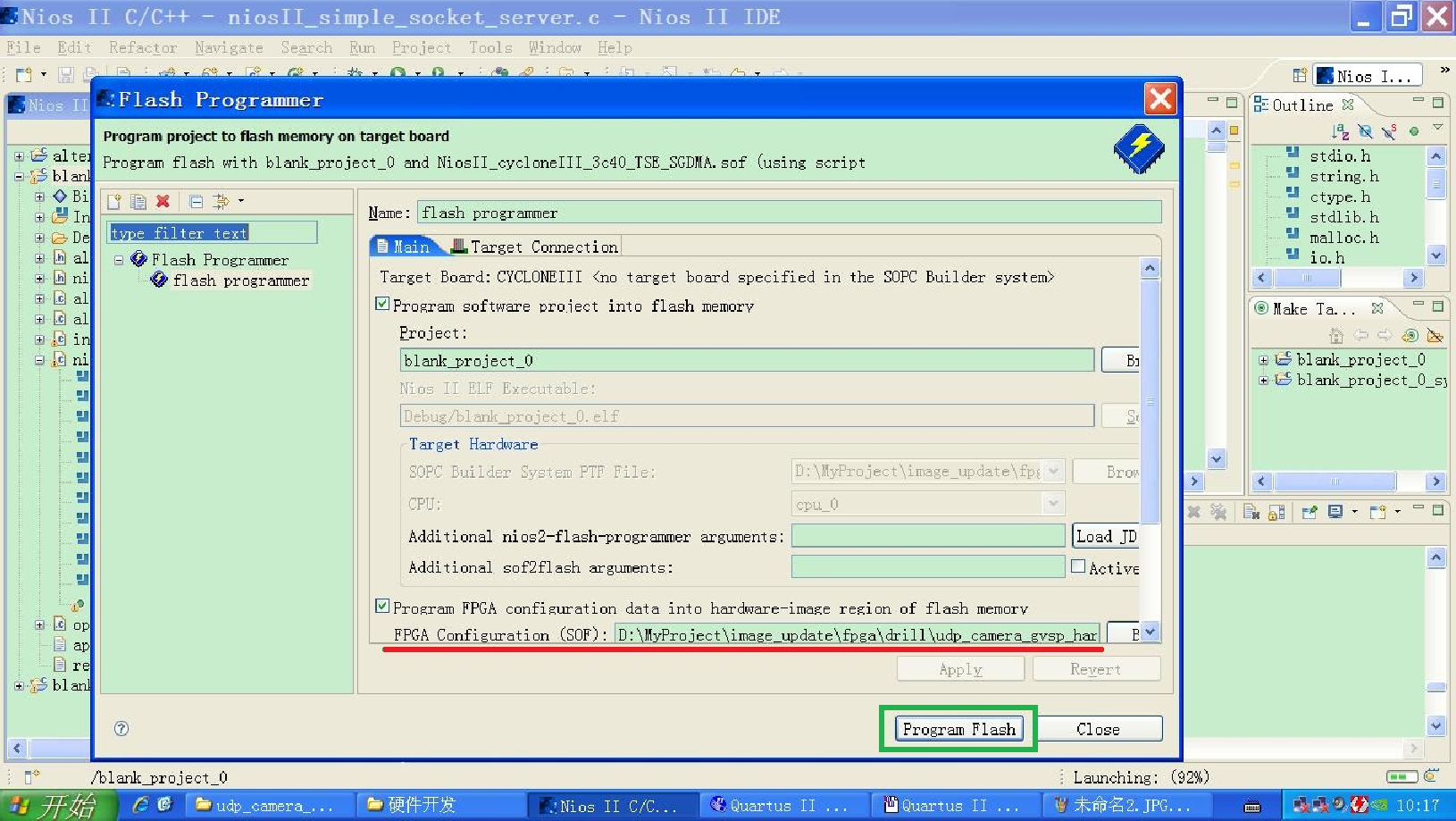

- 打开Tools下的Flash programmer,查看SOF文件路径是否正确,点击最下方的Program Flash烧录,之后断电,拔下仿真器,上电后自动运行。